1. Jurnal [Kembali]

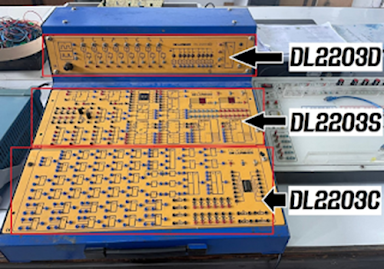

2. Alat dan Bahan [Kembali]

Kelebihan JK Flip-flop adalah tidak adanya kondisi terlarang atau yang berarti di beri berapapun inputan asalkan terdapat clock maka akan terjadi perubahan pada keluarannya / outputnya. berikut adalah symbol dan tabel kebenaran dari JK Flip-Flop.

Pada percobaan 1 terdapat 4 JK Flip-Flop, 2 Switch dan 4 logic probe. Dimana pada rangkaian ini menggunakan dari J dan K maka gerbang dari R dan S haru tidak aktif yatu dengan cara diberi logika 1 atau aktif hight. Sehingga output JK Flip-Flop dipengaruhi oleh input J dan K saja.

Rangkaian percobaan ini merupakan rangkaian asynchronous counter, dikarnakan output JK Flip-Flop dihubungkan pada CLK Flip-Flop selanjutnya. Asyncronous counter disebut juga couter serial dikarnakan output masing-masing Flip-Flop yang dugunakan akan berguling (berubah kondisi dari 0 ke 1) dan sebaliknya secara berurutan demi langkah. Pada rangkaian ini terdapat delay yang disebabkan hanya input CLK Flip-Flop paling ujung yang terhubung dengan CLk, Flip-Flop lainnya diambil dari output sebelumnya. Rangkaian pada percobaan ini digunakan untuk menghitung biner secara aritmatika diamna logicprobe 1 merupakan kode biner 1, logicprobe 2 merupakan binner 2, logicprobe 3 merupakan binner 4, dan logicprobe 4 merupakan binner 8. Karakter yang dihasilkan didapati dari 2n, dimana n merupakan banyaknya Flip-Flop.

1. Analisa output percobaan berdasarkan ic yang digunakan?

Pada percobaan 1, Ic yang digunakan adalah IC JK filp flop sebanyak 4 buah dengan prinsip kerjanya Asyncronus, untuk IC pertama dihubungkan pada clock, outputnya akan berubah sesuai aktif pada clock (aktif low)/fall time. Pada IC berikutnys outputnya akan mengikuti output sebelumnya. Outputnya terakhir akan naik dari 0-15 bertahap.

2. Analisa sinyal output yang dikeluarkan JK flip- flop kedua dan ketiga

Output sinysl dari JK flip-flop kedua hingga keempat diperoleh dari output JK flip-flop sebelumnya.

Pada JK flip-flop kedua akan mem butuhkan 4 kali clock untuk mengubah outputnya. Pada sinyal output JK flip-flop ketiga inputnya H2 dari JK flip-flop kedua yang mana akan berlogika 1 apabila H1 clock pertama berlogika 0 dan JK flip-flop ketiga membutuhkan 8 kali flip -flop.

7. Link Download

[Kembali]

.png)

Tidak ada komentar:

Posting Komentar